### CS 489 / 698: Software and Systems Security

## Module 5: Hardware Security security features, enablers, and accelerators

Meng Xu (University of Waterloo)

Spring 2023

| Intro   | CET         | PA    | MPX     | MTE    | CHERI | <b>RoT</b> |

|---------|-------------|-------|---------|--------|-------|------------|

| ●000    | 00000000000 | 00000 | 0000000 | 000000 | 00000 | 0000       |

| Outline | e           |       |         |        |       |            |

- Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

- 6 Capability Hardware Enhanced RISC Instructions (CHERI)

- Authenticated boot and Root-of-Trust (RoT)

| Intro | CET         | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|-------|-------------|-------|---------|--------|-------|------------|

| 0●00  | 00000000000 | 00000 | 0000000 | 000000 | 00000 | 0000       |

| Motiv | ration      |       |         |        |       |            |

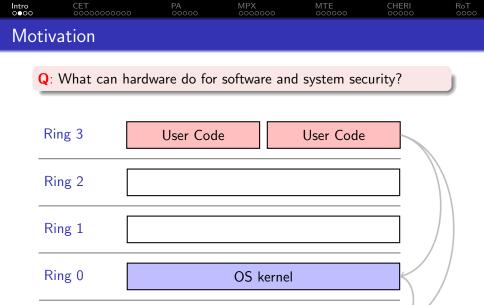

### Q: What can hardware do for software and system security?

| Hardware |

|----------|

|----------|

| Intro  | CET         | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|--------|-------------|-------|---------|--------|-------|------------|

| 00●0   | 00000000000 | 00000 | 0000000 | 000000 | 00000 | 0000       |

| Motiva | ation       |       |         |        |       |            |

**Q**: What can hardware do for software and system security?

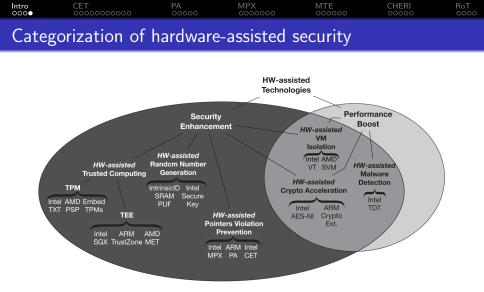

A: There are generally two views on hardware-assisted security:

| Intro | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|-------------|-------|---------|--------|-------|------|

| 00●0  | 00000000000 | 00000 | 0000000 | 000000 | 00000 | 0000 |

| Motiv | ation       |       |         |        |       |      |

**Q**: What can hardware do for software and system security?

A: There are generally two views on hardware-assisted security:

Hardware runs at an even higher privilege level such that a malicious or compromised kernel cannot temper with — e.g., TPMs or TEEs (next lecture)

### Motivation

CET

Intro

**Q**: What can hardware do for software and system security?

A: There are generally two views on hardware-assisted security:

MPX

MTE

CHER

RoT

- Hardware runs at an even higher privilege level such that a malicious or compromised kernel cannot temper with — e.g., TPMs or TEEs (next lecture)

- Hardware can accelerate security mechanisms that are conventionally enforced by kernel, compiler, or even the developers manually — e.g., CHERI (this lecture)

Adapted from survey paper A Comprehensive Survey of Hardware-Assisted Security:

From The Edge to The Cloud

| Intro  | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|--------|-------------|-------|---------|--------|-------|------|

| 0000   | ●0000000000 | 00000 | 0000000 | 000000 | 00000 | 0000 |

| Outlir | ne          |       |         |        |       |      |

- Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

- 6 Capability Hardware Enhanced RISC Instructions (CHERI)

- Authenticated boot and Root-of-Trust (RoT)

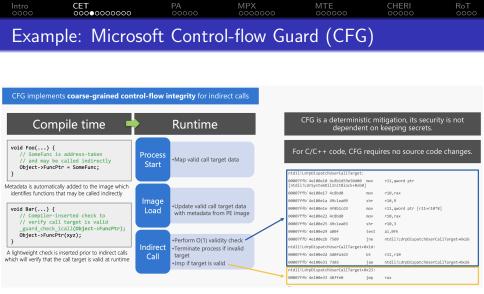

Control-Flow Integrity (CFI) is a classic example of runtime reference monitor in software security.

CFI is also sometimes referred to as program shepherding

monitoring control flow transfers during program execution to enforce a security policy — from a paper in USENIX Security'02.

## Basic ideas of CFI

CET

```

1 void f1():

2 void f2();

3 void f3():

4 void f4(int, int);

\mathbf{5}

void foo(int usr) {

6

void (*func)();

7

8

if (usr == MAGIC)

9

func = f1:

10

else

11

func = f2:

12

13

14

// forward edge CFI check

CHECK_CFI_FORWARD(func);

15

func();

16

17

// backward edge CFI check

18

19

CHECK_CFI_BACKWARD();

20 }

```

Option 1: allow all functions

- f1, f2, f3, f4, foo, printf, system, ...

Option 2: allowed only functions defined in the current module

- f1, f2, f3, f4, foo

Option 3: allow functions with type signature void (\*)()

- f1, f2, f3

Option 4: allow functions whose address are taken (e.g., assigned)

- f1, f2

RoT

Illustration taken from Microsoft Talk: The Evolution of CFI Attacks and Defenses

RFG was our compatible, ABI compliant, performant software shadow stack

RFG relies on a secret: the shadow stack's virtual address

Illustration taken from Microsoft Talk: The Evolution of CFI Attacks and Defenses

Intro

CET

PA

MPX

MTE

CHERI

Rot

RFG deployment experience

Reployment experience

Reployment experience

Reployment experience

Reployment experience

Secrets are bad!

AnC attack (a side-channel attack) could successfully leak where shadow stacks are mapped.

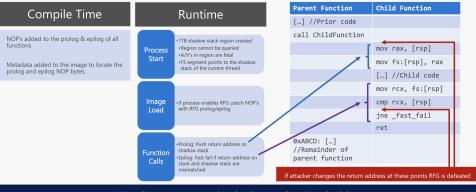

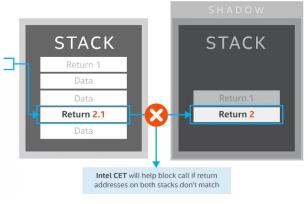

### SHADOW STACK (SS)

SS delivers return address protection to defend against return-oriented programming (ROP) attack methods.

#### Copyright: Intel

# Intro CET PA MPX MTE CHERI RoT CET: shadow stack Stack Stack Stack Stack Stack

- For every regular stack CET adds a shadow stack region, which is indexed via a new register %ssp.

- Regular memory stores (executed from any ring) are not allowed in shadow stack region

When enabled,

- Each time a call instruction gets executed, in addition to the return address being pushed onto the regular stack, a copy of it is also pushed (automatically) onto the shadow stack.

- Each time a ret instruction gets executed, the return addresses pointed by %rsp and %ssp are (automatically) popped from the two stacks, and their values are compared together.

## CET: Indirect Branch Tracking (IBT)

CET introduces a new (4-byte) instruction, i.e., endbr, which becomes the **only** allowed target of indirect call/jmp instructions.

In other words, forward-edge transfers via (indirect) call or jmp instructions are pinned to code locations that are "marked" with an endbr; else, an exception (#CP) is raised.

| Intro | CET            | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|----------------|-------|---------|--------|-------|------|

| 0000  | 00000000000000 | 00000 | 0000000 | 000000 | 00000 | 0000 |

| IBT e | example        |       |         |        |       |      |

```

1 void main() {

2    int (*f) {};

3    f = foo;

4    f();

5  }

6

7 int foo() {

8    return 0;

9 }

```

| 1              | <main>:</main>  |                |                |

|----------------|-----------------|----------------|----------------|

| $^{2}$         | movq            | <b>\$</b> 0x40 | 04fb, -8(%rbp) |

| 3              | mov             | -8 <b>(%r</b>  | bp), %rdx      |

| 4              | call            | *%rdx          |                |

| 5              | :               |                |                |

| 6              | retq            |                |                |

| $\overline{7}$ |                 |                |                |

| 8              | < <u>foo</u> >: |                |                |

| 9              | endbr64         |                |                |

| 10             | :               |                |                |

| 11             | mov             | rax,           | 0              |

| 12             | :               |                |                |

| 13             | retq            |                |                |

| Intro | CET        | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|-------|------------|-------|---------|--------|-------|------------|

| 0000  | 0000000000 | 00000 | 0000000 | 000000 | 00000 | 0000       |

| IBT e | example    |       |         |        |       |            |

| 1              | voi | 1 main() {              |

|----------------|-----|-------------------------|

| $^{2}$         |     | <b>int</b> (*f) {};     |

| 3              |     | <pre>int (*g) {};</pre> |

| 4              |     | f = foo;                |

| <b>5</b>       |     | g = bar;                |

| 6              |     | f();                    |

| $\overline{7}$ |     | g();                    |

| 8              | }   |                         |

| 9              |     |                         |

| 10             | int | <pre>foo() {</pre>      |

| 11             |     | <pre>return 0;</pre>    |

| 12             | }   |                         |

| 13             |     |                         |

| 14             | int | <pre>bar() {</pre>      |

| 15             |     | return 1;               |

| 16             | }   |                         |

|                |     |                         |

| 1<br>2 | main>:       | <b>\$</b> 0x4004fb, -16(%rbp) |

|--------|--------------|-------------------------------|

|        | movq         | -16(%rbp), %rdx               |

|        |              | *%rdx                         |

|        |              | -8(%rbp), %rdx                |

|        |              | *%rdx                         |

|        |              | ,oi un                        |

|        | retq         |                               |

| 9      | 1004         |                               |

|        | <foo>:</foo> |                               |

| 11     | endbr64      |                               |

| 12     | _            |                               |

|        |              | rax, 0                        |

| 14     | _            | 2411, 0                       |

|        | retq         |                               |

| 16     | 1004         |                               |

| 17     | <br>bar>:    |                               |

| 18     | endbr64      |                               |

| 19     |              |                               |

|        |              | rax, 1                        |

| 21     |              | , -                           |

| 22     |              |                               |

|        | 1            |                               |

| Intro<br>0000 | CET<br>00000000000 | PA<br>●0000 | MPX<br>0000000 | MTE<br>000000 | CHERI<br>00000 | <b>R₀T</b><br>0000 |

|---------------|--------------------|-------------|----------------|---------------|----------------|--------------------|

| Outli         | ne                 |             |                |               |                |                    |

|               |                    |             |                |               |                |                    |

- 2 Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

- 6 Capability Hardware Enhanced RISC Instructions (CHERI)

- Authenticated boot and Root-of-Trust (RoT)

| Intro | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | ○●○○○ | 0000000 | 000000 | 00000 | 0000 |

| Motiv | vation      |       |         |        |       |      |

| Intro | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | ○●○○○ | 0000000 | 000000 | 00000 | 0000 |

| Motiv | vation      |       |         |        |       |      |

- i.e., the value of the pointer remains unchanged, not the memory content referred to by this pointer.

- i.e., the value of the pointer remains unchanged, not the memory content referred to by this pointer.

- Perfect code pointer integrity implies control-flow integrity (CFI).

- i.e., the value of the pointer remains unchanged, not the memory content referred to by this pointer.

- Perfect code pointer integrity implies control-flow integrity (CFI).

Data pointer integrity is also important (e.g., against data-only attacks and data-oriented programming) and can be (partially) achieved via Pointer Authentication.

| Intro | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | 00●00 | 0000000 | 000000 | 00000 | 0000 |

| Overv | view        |       |         |        |       |      |

Available since Armv8.3-A instruction set architecture (ISA) when the processor executes in 64-bit Arm state (AArch64)

PA consists of a set of instructions for creating and authenticating pointer authentication codes (PACs).

| Intro | CET         | PA    | MPX     | MTE    | CHERI | RoT  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | 000●0 | 0000000 | 000000 | 00000 | 0000 |

| PAC d | letails     |       |         |        |       |      |

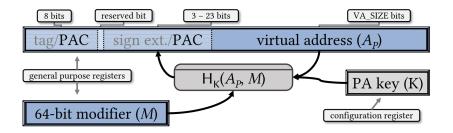

- Each PAC is derived from

- A pointer value

- A 64-bit context value (modifier)

- A 128-bit secret key

| Intro | CET         | PA    | MPX     | MTE    | CHERI | RoT  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | 000●0 | 0000000 | 000000 | 00000 | 0000 |

| PAC d | letails     |       |         |        |       |      |

- Each PAC is derived from

- A pointer value

- \* an N-bit memory address

- A 64-bit context value (modifier)

- \* doesn't need to secret, as long as it provides enough entropy

- A 128-bit secret key

- \* held in system registers, set by the kernel per each process,

- $^{*}$  can be used, but cannot be read/written by userspace

| Intro | CET         | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|-------|-------------|-------|---------|--------|-------|------------|

| 0000  | 00000000000 | 000●0 | 0000000 | 000000 | 00000 | 0000       |

| PAC d | etails      |       |         |        |       |            |

- Each PAC is derived from

- A pointer value

- \* an N-bit memory address

- A 64-bit context value (modifier)

- $\ast$  doesn't need to secret, as long as it provides enough entropy

- A 128-bit secret key

- \* held in system registers, set by the kernel per each process,

- $^{st}$  can be used, but cannot be read/written by userspace

- PAC essentially a key-ed message authentication code (MAC) where the MAC algorithm can be implementation defined

- by default, it is QARMA

- Instructions hide the algorithm details (sign + authenticate)

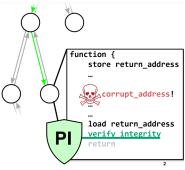

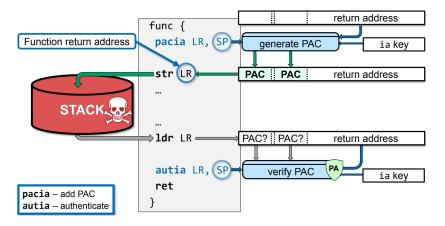

## Example: PA-based return address signing

Deployed as -msign-return-address in GCC and LLVM/Clang

| Intro   | CET         | PA    | MPX     | MTE    | CHERI | RoT  |

|---------|-------------|-------|---------|--------|-------|------|

| 0000    | 00000000000 | 00000 | ●000000 | 000000 | 00000 | 0000 |

| Outline | e           |       |         |        |       |      |

- 2 Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

- 6 Capability Hardware Enhanced RISC Instructions (CHERI)

- Authenticated boot and Root-of-Trust (RoT)

| Intro   | CET         | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|---------|-------------|-------|---------|--------|-------|------------|

| 0000    | 00000000000 | 00000 | 0●00000 | 000000 | 00000 | 0000       |

| Brief h | nistory     |       |         |        |       |            |

Intel MPX (Memory Protection Extensions) was a set of extensions to the x86 instruction set architecture to perform bounds checking.

Intro

Intel MPX (Memory Protection Extensions) was a set of extensions to the x86 instruction set architecture to perform bounds checking.

MPX

MTE

- 2013-07: Intel introduces MPX in its ISA manual

- 2015-02: Linux kernel adds support to MPX in its 3.19 release

- 2015-04: GCC adds support to MPX in its 5.0 release

- 2015-08: MPX becomes available in Skylake microarchitecture

- 2018-06: An important paper Intel MPX Explained: A Cross-layer Analysis of the Intel MPX System Stack was published.

- 2019-??: Intel removes MPX from its ISA manual

- 2019-05: GCC drops support for MPX in its 9.1 release

- 2020-03: Linux kernel drops support for MPX in its 5.6 release

RoT

| Intro<br>0000      | CET<br>00000000000 | PA<br>00000 | MPX<br>00●0000 | MTE<br>000000 | CHERI<br>00000 | RoT<br>0000 |  |  |  |

|--------------------|--------------------|-------------|----------------|---------------|----------------|-------------|--|--|--|

| How does MPX work? |                    |             |                |               |                |             |  |  |  |

| 2 ol               | truct obj {        | tal = 0;    | -              |               |                |             |  |  |  |

#### MPX 0000000 How does MPX work? 1 struct obj { char buf[100]; int len } 2 obj\* a[10]; total = 0; 3 for (i=0; i<M; i++) { total += a[i]->len; } **for** (i=0; i<M; i++): 1 ai = a + i// Pointer arithmetic on a 2 objptr = load ai // Pointer to obj at a[i] 3 lenptr = objptr + 100 // Pointer to obj.len 4 len = load lenptr 5

6 total += len // Total length of all objs

```

MPX

000000

How does MPX work?

1 struct obj { char buf[100]; int len }

2 obj* a[10]; total = 0;

3 for (i=0; i<M; i++) { total += a[i]->len; }

for (i=0; i<M; i++):

1

ai = a + i

// Pointer arithmetic on a

2

objptr = load ai // Pointer to obj at a[i]

3

lenptr = objptr + 100 // Pointer to obj.len

4

len = load lenptr

5

total += len

6

// Total length of all obis

1 a_b = bndmk a, a+79

for (i=0; i<M; i++):

2

ai = a + i

3

bndcl a_b, ai

// Lower-bound check of a[i]

4

bndcu a_b, ai+7

// Upper-bound check of a[i]

5

objptr = load ai

6

objptr_b = bndldx ai

// Bounds for pointer at a[i]

7

lenptr = objptr + 100

8

bndcl objptr_b, lenptr // Lower-bound check of obj.len

9

10

bndcu objptr_b, lenptr+3 // Upper-bound check of obj.len

len = load lenptr

11

12

total += len

```

Intro

CET

PA

MPX

MTE

CHERI

RoT

Occore

spatial safety

Spatial safety

Spatial safety

Spatial safety

Spatial safety

At any point of time during the program execution, for any object in memory, we know its (**object\_id**, size [int], alive [bool])

At the same time, for each memory access, we know:

- Memory read: (object\_id, offset [int], length [int])

- Memory write: (object\_id, offset [int], length [int], \_)

It is a violation of spatial safety if:

offset + length >= size or

• offset < 0

## Intro CET PA MPX MTE CHERI RoT Supporting MPX ODDOOLOOD ODDOOLOOD</td

Adopting Intel MPX requires modifications at each level of the hardware-software stack:

• At the hardware level,

- At the kernel level:

- At the compiler level,

• At the application level,

## Intro CET PA MPX MTE CHERI RoT Supporting MPX ODDOOLOOD ODDOOLOOD</td

Adopting Intel MPX requires modifications at each level of the hardware-software stack:

- At the hardware level,

- new instructions

- a set of 128-bit registers (why 128-bit?)

- the #BR exception thrown by these new instructions

- At the kernel level:

• At the compiler level,

• At the application level,

####

Adopting Intel MPX requires modifications at each level of the hardware-software stack:

- At the hardware level,

- new instructions

- a set of 128-bit registers (why 128-bit?)

- the #BR exception thrown by these new instructions

- At the kernel level: a new #BR exception handler for

- allocating storage for bounds on-demand, and

- sending a signal to the program upon bound violation.

- At the compiler level,

• At the application level,

## Intro CET PA MPX MTE CHERI RoT Supporting MPX ODDO<000</td> ODDO<000</td> ODDO<000</td> ODDO ODDO</

Adopting Intel MPX requires modifications at each level of the hardware-software stack:

- At the hardware level,

- new instructions

- a set of 128-bit registers (why 128-bit?)

- the #BR exception thrown by these new instructions

- At the kernel level: a new #BR exception handler for

- allocating storage for bounds on-demand, and

- sending a signal to the program upon bound violation.

- At the compiler level,

- new MPX transformation passes

- new runtime libraries for initialization/finalization routines, debug information, and bridges to other non-MPX-protected libraries.

- At the application level,

# Intro CET PA MPX MTE CHERI RoT Supporting MPX ODDO<000</td> ODDO<000</td> ODDO<000</td> ODDO ODDO</

Adopting Intel MPX requires modifications at each level of the hardware-software stack:

- At the hardware level,

- new instructions

- a set of 128-bit registers (why 128-bit?)

- the #BR exception thrown by these new instructions

- At the kernel level: a new #BR exception handler for

- allocating storage for bounds on-demand, and

- sending a signal to the program upon bound violation.

- At the compiler level,

- new MPX transformation passes

- new runtime libraries for initialization/finalization routines, debug information, and bridges to other non-MPX-protected libraries.

- At the application level,

- manual change of troublesome C coding patterns

- multithreading issues

- interaction with other ISA extensions (e.g., TSX and SGX).

| Intro | CET         | PA    | MPX     | MTE    | CHERI | RoT  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | 00000 | 00000●0 | 000000 | 00000 | 0000 |

| What  | do we gain? |       |         |        |       |      |

| Approach                                   | Detects                   | <b>RIPE</b> bugs | Other bugs   | Broken         | Perf (×)           |

|--------------------------------------------|---------------------------|------------------|--------------|----------------|--------------------|

| Native: no protection                      | -                         | <b>64</b> (34)   | 6 (3)        | <b>0</b> (0)   | <b>1.00</b> (1.00) |

| MPX security levels:                       |                           |                  |              |                |                    |

| L1: only-writes and no narrowing of bounds | inter-object overwrites   | <b>14</b> (14)   | 3 (0)        | 3 (5)          | <b>1.29</b> (1.18) |

| L2: no narrowing of bounds                 | + inter-object overreads  | <b>14</b> (14)   | 3 (0)        | 2 (8)          | <b>2.39</b> (1.46) |

| L3: only-writes and narrowing of bounds    | all overwrites*           | 14 (0)           | 2 (0)        | 4 (7)          | <b>1.30</b> (1.19) |

| L4: narrowing of bounds (default)          | + all overreads*          | 14 (0)           | <b>0</b> (0) | 4 (9)          | <b>2.52</b> (1.47) |

| L5:+ fchkp-first-field-has-own-bounds *    | + all overreads           | 0 (-)            | 0 (-)        | 6 (-)          | 2.52 (-)           |

| L6: + BNDPRESERVE=1 (protect all code)     | all overflows in all code | <b>O</b> (O)     | <b>O</b> (O) | <b>34</b> (29) | -                  |

| AddressSanitizer                           | inter-object overflows    | 12               | 3            | 0              | 1.55               |

\* except intra-object overwrites & overreads through the first field of struct, level 5 removes this limitation (only relevant for GCC version)

#### Evaluation results available on this website

####

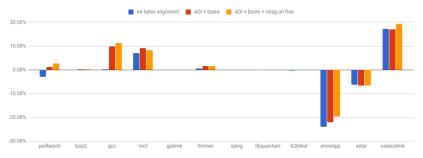

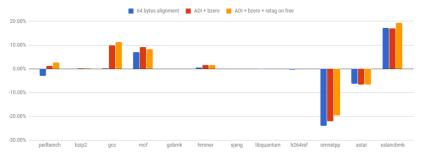

- New MPX instructions are not as fast as expected

- The average overhead of 20-50% is not significantly better than ASan

- The supporting infrastructure is not mature enough

- MPX transformation in compilers might be buggy

- Other libraries needs to have MPX-enabled

- MPX provides no temporal protection

- ASan has partial support

- MPX does not support multithreading transparently

- Both false positives and false negatives if the application does not conform to C11 memory model or if the compiler does not update bounds in atomic primitives

- MPX is not compatible with some C idioms

- e.g., using a struct field (usually the first field of struct) to access other fields of the struct

- custom memory management, e.g., arbitrary type casts and in-pointer bit twiddling

| Intro  | CET         | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|--------|-------------|-------|---------|--------|-------|------------|

| 0000   | 00000000000 | 00000 | 0000000 | ●00000 | 00000 | 0000       |

| Outlir | ne          |       |         |        |       |            |

- 2 Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

- 6 Capability Hardware Enhanced RISC Instructions (CHERI)

- Authenticated boot and Root-of-Trust (RoT)

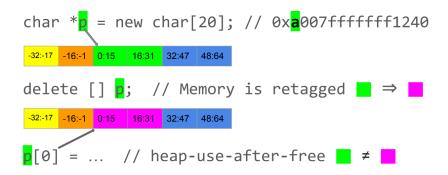

Introduced into the Armv8.5-A instruction set architecture (ISA) as Memory Tagging Extension (MTE) in 2018.

- 64-bit architecture only (AArch64)

- As a hardware accelerator for detecting memory errors

Introduced into the Armv8.5-A instruction set architecture (ISA) as Memory Tagging Extension (MTE) in 2018.

- 64-bit architecture only (AArch64)

- As a hardware accelerator for detecting memory errors

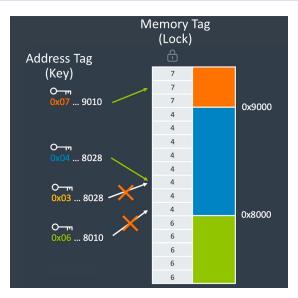

MTE implements a "lock-and-key" scheme for memory access:

- Two types of tags:

- Every aligned 16 bytes of memory have a 4-bit tag stored separately, i.e., not addressable (the "lock")

- Every pointer has a 4-bit tag stored in the top byte (the "key")

- LD/ST instructions check both tags, raise exception on mismatch

- New instructions are introduced to manipulate the tags

Source: article Delivering enhanced security through Memory Tagging Extension 31/43

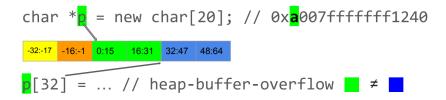

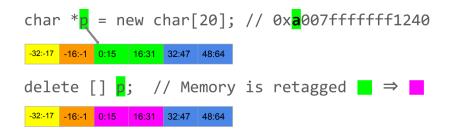

## Intro CET PA MPX MTE CHERI RoT Detecting heap overflow Overflow

### Detecting heap overflow

MTE 0000000

### Adoption in practice

• LLVM MemTagSanitizer detects a similar class of errors as AddressSanitizer or HardwareAssistedAddressSanitizer, but with **much** lower overhead.

MTE

00000

Source of numbers: LLVM whitepaper on memory tagging

RoT

### Adoption in practice

CET

• LLVM MemTagSanitizer detects a similar class of errors as AddressSanitizer or HardwareAssistedAddressSanitizer, but with **much** lower overhead.

MPX

MTE

Source of numbers: LLVM whitepaper on memory tagging

• In Android 12, the kernel and userspace heap memory allocator can augment each allocation with metadata, based on this article.

RoT

| Intro  | CET         | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|--------|-------------|-------|---------|--------|-------|------------|

| 0000   | 00000000000 | 00000 | 0000000 | 000000 | ●0000 | 0000       |

| Outlir | ne          |       |         |        |       |            |

- 2 Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

6 Capability Hardware Enhanced RISC Instructions (CHERI)

Authenticated boot and Root-of-Trust (RoT)

| Intro  | CET          | PA    | MPX     | MTE    | CHERI | <b>R₀T</b> |

|--------|--------------|-------|---------|--------|-------|------------|

| 0000   | 00000000000  | 00000 | 0000000 | 000000 | o●ooo | 0000       |

| Re-def | ining pointe | rs    |         |        |       |            |

A pointer is not only an *N*-bit value representing a memory address, rather, it is a capability granting certain permissions to access a restrictive range in the memory address space.

| Intro | CET         | PA       | MPX     | MTE    | CHERI | RoT  |

|-------|-------------|----------|---------|--------|-------|------|

| 0000  | 00000000000 | 00000    | 0000000 | 000000 | 00●00 | 0000 |

| CHFR  | l memory ca | nability |         |        |       |      |

|                      | 1 - valid d<br>0 - invalid t |                                              | 15-bit:<br>defines if and how<br>the capability is sealed |                                                              | 64-bit:<br>56-bit bounds and<br>flag. This is offset<br>the Bounds field |   |

|----------------------|------------------------------|----------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|---|

| $\operatorname{Bit}$ | 128 1                        | 27 1                                         | .09 9                                                     | 6                                                            | 3                                                                        | 0 |

|                      | Tag                          | Permissions                                  | Object type                                               | Bounds                                                       | Value                                                                    |   |

|                      |                              | 18-bit:<br>limits usage<br>of the capability |                                                           | 87-bit bound, limit<br>the scope of the ca<br>(31 + 56 bits) |                                                                          |   |

A "pointer", or rather, a memory capability, in the view of the CHERI Morello architecture (source of image: Pawel Zalewski's blog post).

| Intro | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | 00000 | 0000000 | 000000 | 000●0 | 0000 |

| CHERI | basic idea  |       |         |        |       |      |

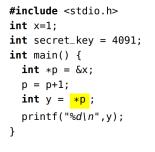

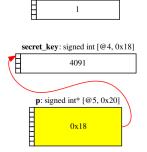

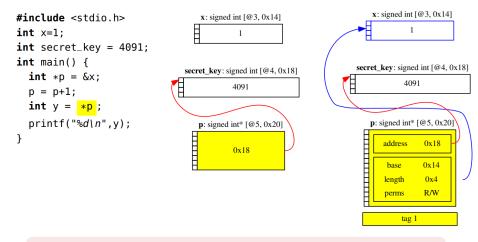

```

#include <stdio.h>

int x=1;

int secret_key = 4091;

int main() {

int *p = &x;

p = p+1;

int y = *p;

printf("%d\n",y);

}

```

| Intro | CET          | PA    | MPX     | MTE    | CHERI | RoT  |

|-------|--------------|-------|---------|--------|-------|------|

| 0000  | 00000000000  | 00000 | 0000000 | 000000 | 000●0 | 0000 |

| CHER  | l basic idea |       |         |        |       |      |

```

#include <stdio.h>

int x=1;

int secret_key = 4091;

int main() {

int *p = &x;

p = p+1;

int y = *p;

printf("%d\n",y);

}

```

#### **Q**: What will happen?

x: signed int [@3, 0x14]

### **Q**: What will happen?

### **Q**: What will happen?

# Intro CET PA MPX MTE CHERI RoT OCCOO OCCOO OCCOO OCCOO OCCOO OCCOO OCCOO CHERI software stack CHERI software stack CHERI software stack CHERI software stack CHERI software stack

Completely re-vamped software stack:

- Compilers: *custom-made* Clang/LLVM

- Operating systems: hand-tuned FreeBSD, FreeRTOS

- Applications: ported WebKit, OpenSSH, and PostgreSQL

| Intro  | CET         | PA    | MPX     | MTE    | CHERI | RoT  |

|--------|-------------|-------|---------|--------|-------|------|

| 0000   | 00000000000 | 00000 | 0000000 | 000000 | 00000 | ●000 |

| Outlir | าย          |       |         |        |       |      |

- 2 Intel Control-flow Enforcement Technology (CET)

- 3 Arm Pointer Authentication (PA)

- Intel Memory Protection Extensions (MPX)

- 5 Arm Memory Tagging Extension (MTE)

- 6 Capability Hardware Enhanced RISC Instructions (CHERI)

- Authenticated boot and Root-of-Trust (RoT)

| Intro | CET         | PA    | MPX     | MTE    | CHERI | R₀T  |

|-------|-------------|-------|---------|--------|-------|------|

| 0000  | 00000000000 | 00000 | 0000000 | 000000 | 00000 | 0●00 |

| Overv | iew         |       |         |        |       |      |

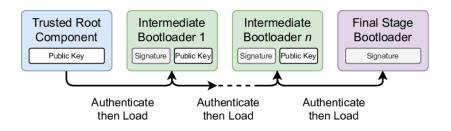

**Goal**: ensures only trusted and authenticated software (e.g., firmware, kernel, application) runs on a computing system.

**Goal**: ensures only trusted and authenticated software (e.g., firmware, kernel, application) runs on a computing system.

An abstract view of the authenticated boot process

### Requirements for the root-of-trust (RoT) component

- Boot process is guaranteed to start from the RoT component

- The cryptographic key is non-readable, non-writable at any privilege level

- The only way to use the key is to verify the signature via special hardware instructions.

- The RoT component, upon booting, must first measure the code content of the first stage bootloader and validate the measurement with the signature.

### Intro CET PA MPX MTE CHERI Rot Requirements for the root-of-trust (RoT) component Comp

- Boot process is guaranteed to start from the RoT component

- The cryptographic key is non-readable, non-writable at any privilege level

- The only way to use the key is to verify the signature via special hardware instructions.

- The RoT component, upon booting, must first measure the code content of the first stage bootloader and validate the measurement with the signature.

Usually, the RoT component is encapsulated in a hardware module named Hardware Security Module (HSM).

|  | Intro<br>0000 | CET<br>00000000000 | PA<br>00000 | MPX<br>0000000 | MTE<br>000000 | CHERI | <b>RoT</b><br>000● |

|--|---------------|--------------------|-------------|----------------|---------------|-------|--------------------|

|--|---------------|--------------------|-------------|----------------|---------------|-------|--------------------|

### $\langle$ End $\rangle$