# AUTOMATIC GENERATION OF LOGIC DIAGRAMS

bу

James A. Smith

Research Report CS-76-26

Department of Computer Science

University of Waterloo Waterloo, Ontario, Canada May 1976

# ACKNOWLEDGEMENTS

This report is based on the Ph.D. thesis "Automated Generation of Logic Diagrams" by J.A. Smith, October 1975. The guidence and support of Dr. J.G. Linders through this research project is gratefully acknowledged. This work was supported in part by the National Research Council under grant NRC A7640.

#### ABSTRACT

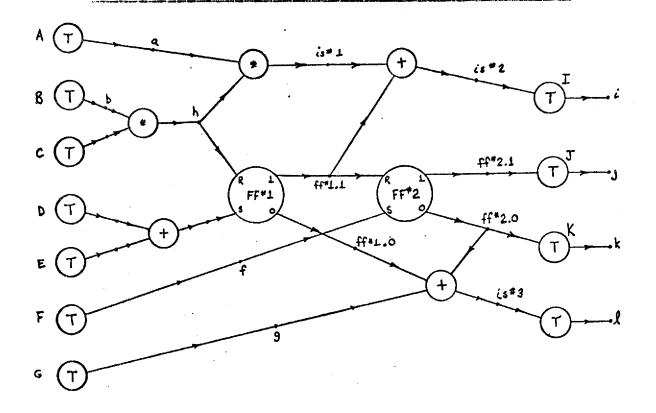

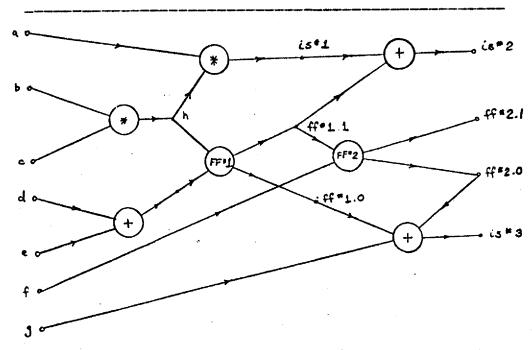

This report studies the automated generation of logic diagrams. Logic diagrams play an important role in the design, development and maintenance of logic circuitry. The automated production of logic diagrams results in increased speed and accuracy.

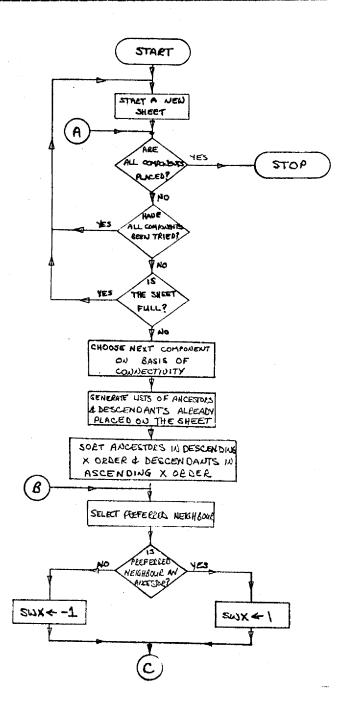

This report discusses the logic diagram problem and gives a set of objectives and requirements that automated logic diagram generation system (ALDGS) should meet. The structural information of a logic circuit is represented by graphs and new methods are developed for classifying and transforming this information for use in the generation of logic diagrams. The steps involved in automatically generating a logic diagram are: partitioning the logic circuit, placement of components on the sheet, and routing the interconnections between the components. Methods are given for partitioning and placing the logic circuit elements on a logic diagram sheet and objective criteria are established for evaluating the placement. A which reduces given routing algorithm is interconnection crossings on the logic diagram.

The algorithms and techniques have been implemented in a system which takes a pseudo-boolean representation of a circuit and generates the appropriate logic diagram(s). Examples are given of several circuits for which the system has generated the logic diagrams automatically.

# TABLE OF CONTENTS

|                                                                                    | Page  |

|------------------------------------------------------------------------------------|-------|

| Chapter 0. Introduction                                                            |       |

| 0.0 Introduction                                                                   | 0.1   |

| Chapter 1. The logic Diagram Layout Problem                                        |       |

| 1.0 Introduction                                                                   | 1 • 1 |

| 1.1 The Logic Diagram Layout System                                                | 1 • 1 |

| 1.2 Information to be Presented                                                    | 1.2   |

| 1.3 Analysis of the Problem                                                        | 1 • 4 |

| 1.4 Cost                                                                           | 1.5   |

| 1.4.1 General Considerations 1.4.2 Interaction                                     | 1.6   |

| 1.5 Summary of Desirable Features for LD Layout                                    | 1.7   |

| Chapter 2. Survey of Related Work                                                  |       |

| 2.0 Introduction                                                                   | 2.1   |

| 2.1 Logic Diagram Generation Systems and Their Capabilities                        |       |

| 2.1.1 IBM and Fujitsu                                                              | 2.2   |

| 2.1.2 Bell Telephone Laboratories                                                  | 2.6   |

| 2.1.3 General Electric                                                             | 2.9   |

| 2.1.4 Sperry-Rand                                                                  | 2.11  |

| 2.1.5 Sanders                                                                      | 2•13  |

| 2.2 A Survey of Techniques for LD Generation and                                   |       |

| Related Problems                                                                   | 2.15  |

| 2.2.1 Partitioning                                                                 | 2.17  |

| 2.2.2 Placement                                                                    | 2.17  |

| 2.2.3 Routing Schemes                                                              | 2.19  |

| 2.3 Summary                                                                        | 2.22  |

| Chapter 3. Representation of the Logic Circuit and the Logic Diagram Configuration |       |

| 3.0 Introduction                                                                   | 3.1   |

| 3.1 Definitions                                                                    | 3.2   |

| 3.2 The Logic Circuit and Its Environment                                                                                                           | 3.3                          |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---|

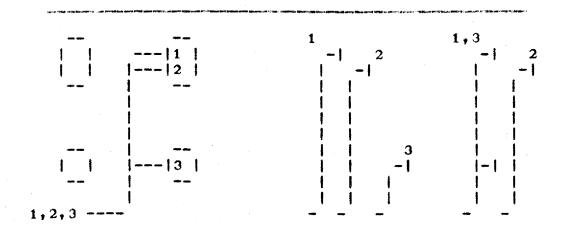

| 3.3 Representative Graphs                                                                                                                           | 3.4                          |   |

| 3.4 Reduced Graphs                                                                                                                                  | 3.6                          |   |

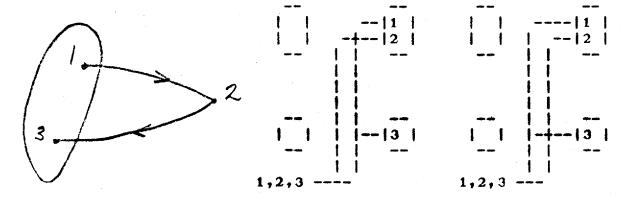

| 3.5 Partitioning the Reduced Graph                                                                                                                  | 3.8                          |   |

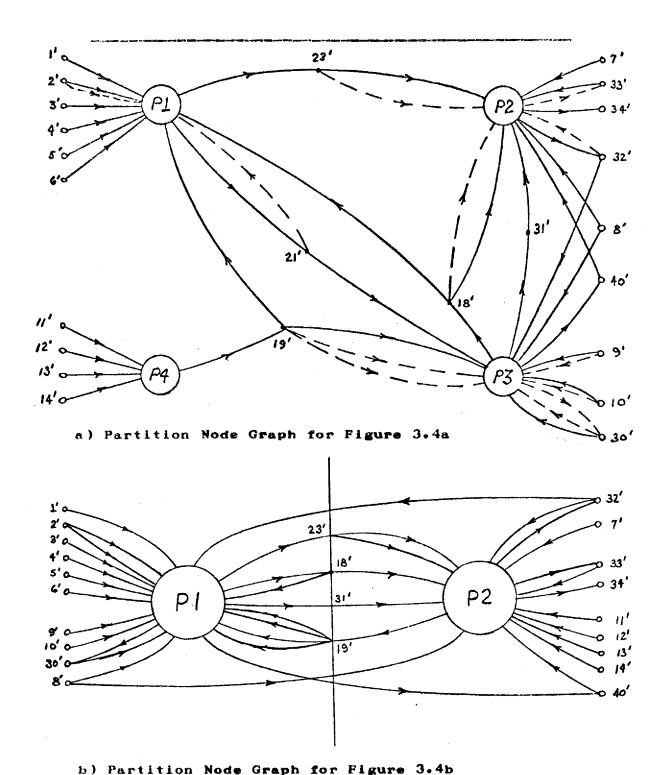

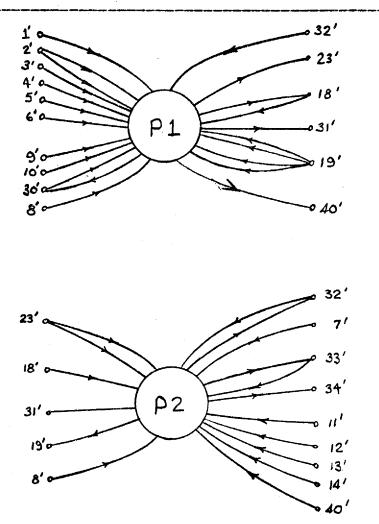

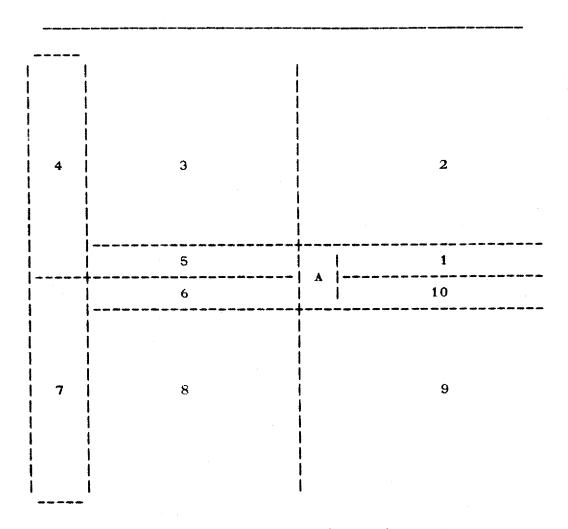

| 3.6 Partition Node Graphs                                                                                                                           | 3.8                          |   |

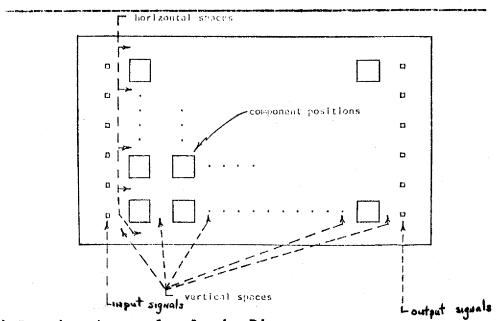

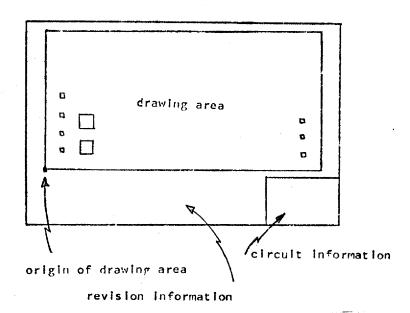

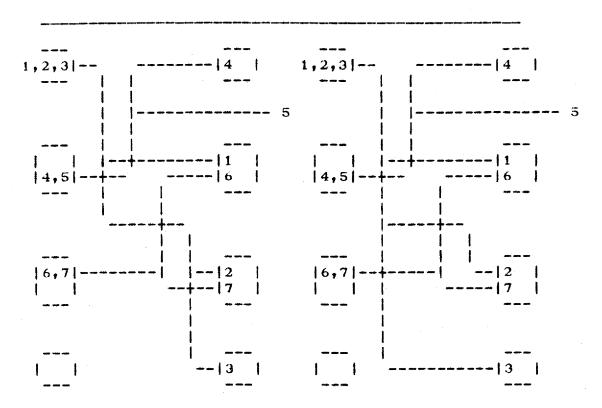

| 3.7 Sheet Node Graphs and Sheet Graphs                                                                                                              | 3.11                         |   |

| 3.8 The Logic Diagram                                                                                                                               | 3.14                         |   |

| Chapter 4. Placement and Pin Assignment for Logic Diagrams                                                                                          |                              |   |

| 4.0 Introduction                                                                                                                                    | 4.1                          |   |

| 4.1 Placement                                                                                                                                       | 4.1                          |   |

| 4.1.1 Initial Placement                                                                                                                             | 4.2                          |   |

| 4.1.2 Placement Refinement                                                                                                                          | 4.6                          |   |

| 4.2 Placement of Boundary Signal Nodes and Pin Assignment 4.2.1 Boundary Input Signal Nodes 4.2.2 Boundary Output Signal Nodes 4.2.3 Pin Assignment | 4.14<br>4.16<br>4.22<br>4.24 |   |

| Chapter 5. A New Routing Technique for Logic Diagrams                                                                                               |                              |   |

| 5.0 Introduction                                                                                                                                    | 5.1                          |   |

| 5.1 Definitions                                                                                                                                     | 5.1                          |   |

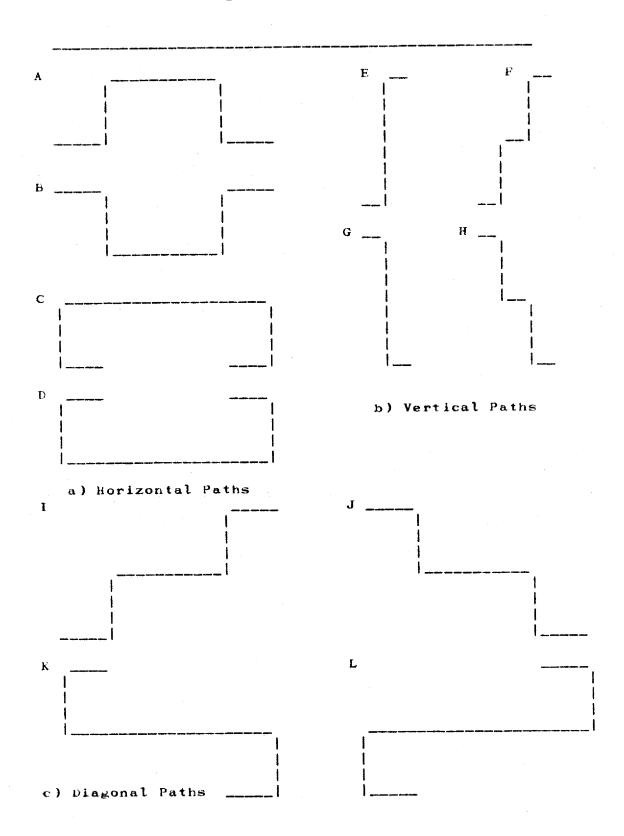

| 5.2 Paths                                                                                                                                           | 5.0                          |   |

| 5.2.1 Classification of Paths 5.2.2 Assignment of Connections to Paths                                                                              | 5 • 2<br>5 • 4               |   |

| E 2 Sagman to                                                                                                                                       |                              |   |

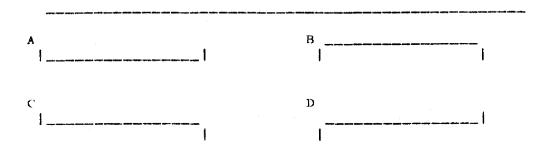

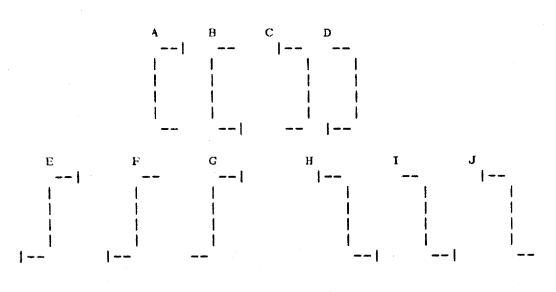

| 5.3.Segments 5.3.1 Segments of Paths                                                                                                                | 5.4                          | - |

| 5.3.2 Intersection of Segments                                                                                                                      | 5.5                          |   |

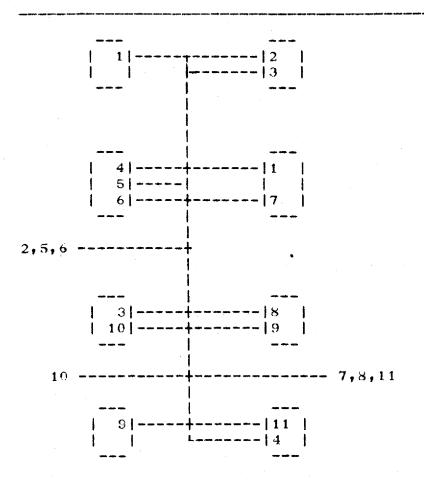

| 5.3.3 Assignment of Segments to Channels,                                                                                                           |                              |   |

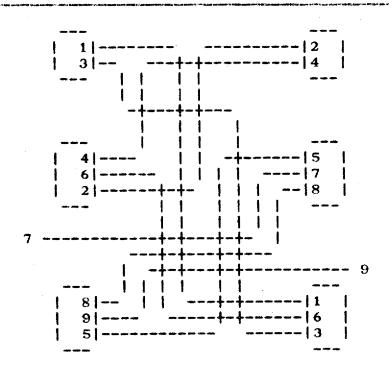

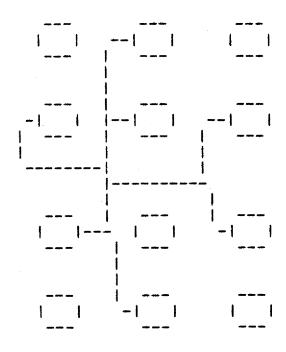

| Fxample 5.1                                                                                                                                         | 5•7                          |   |

| 5.3.4 Correction of Conflict Situations                                                                                                             |                              |   |

| Using Segments                                                                                                                                      | 5.13                         |   |

| 5.3.5 Assignment of Segments to Channels,                                                                                                           |                              |   |

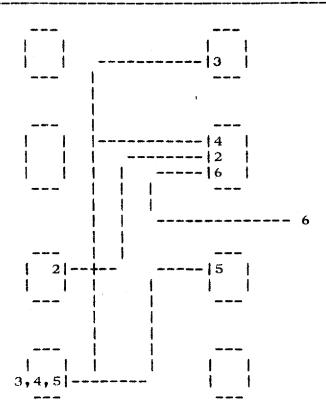

| Example 5.2                                                                                                                                         | 5.15                         |   |

| 5.3.6 Algorithms for Assignment of Segments to Channels                                                                                             | 5.20                         |   |

|                                                                                                                                                     |                              |   |

|                                                                                                                                                     |                              | • |

|                                                                                                                                                     |                              | 1 |

|                                                                                                                                                     |                              |   |

| 5.4 Nets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.24           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

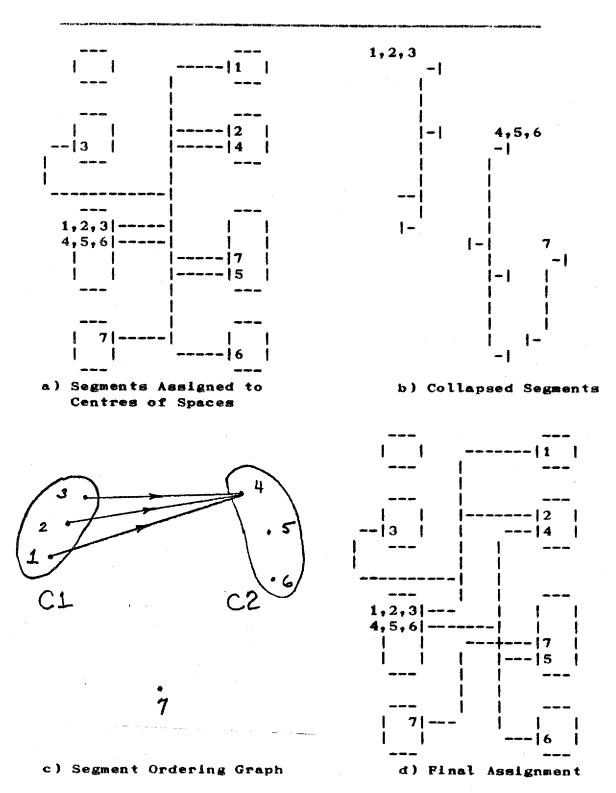

| 5.4.1 Collapsing of Simple Segments into                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| Compound Segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.26           |

| 5.4.2 Assignment of Simple and Compound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| Segments to Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.27           |

| 5.4.3 Nets and Non-Acyclic Segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| Ordering Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.28           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Chapter 6. Results, Conclusions and Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| for Future Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | *              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| 6.0 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.1            |

| 6 1 Commiss of Automotically Deadword Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

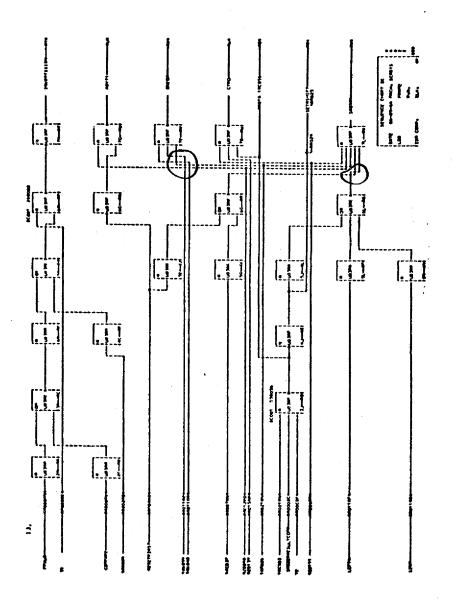

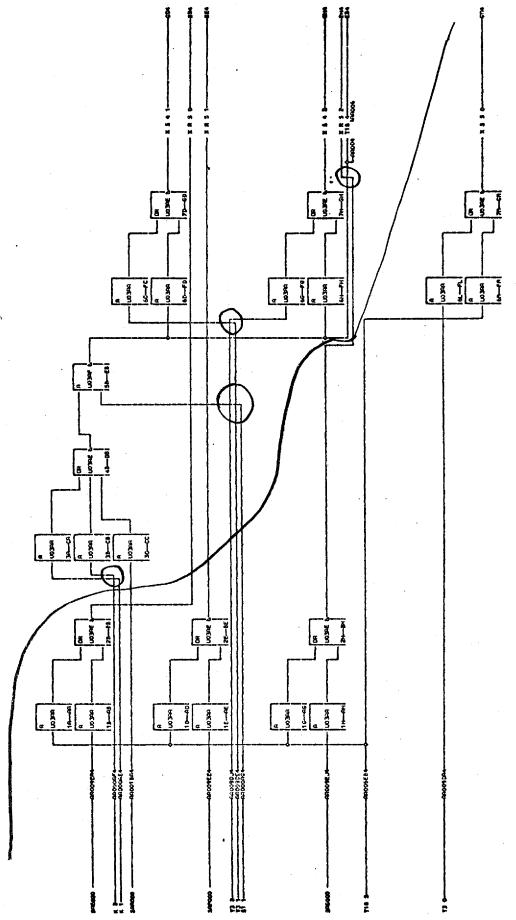

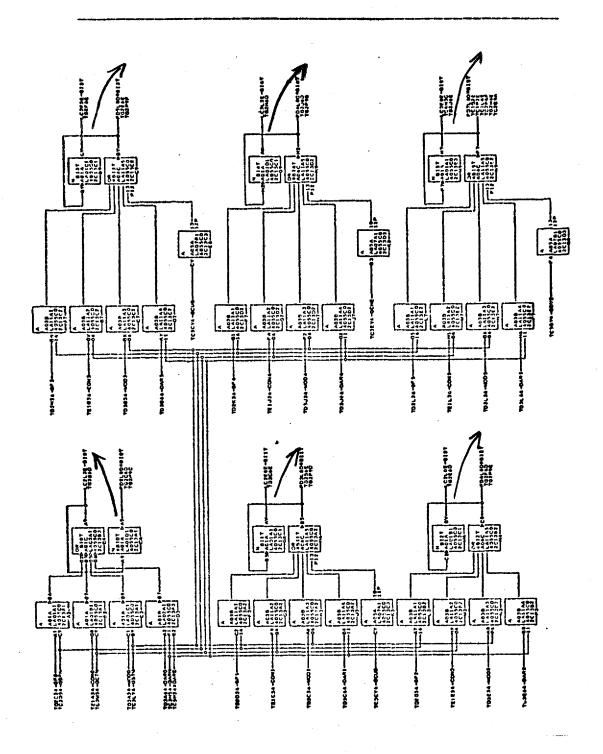

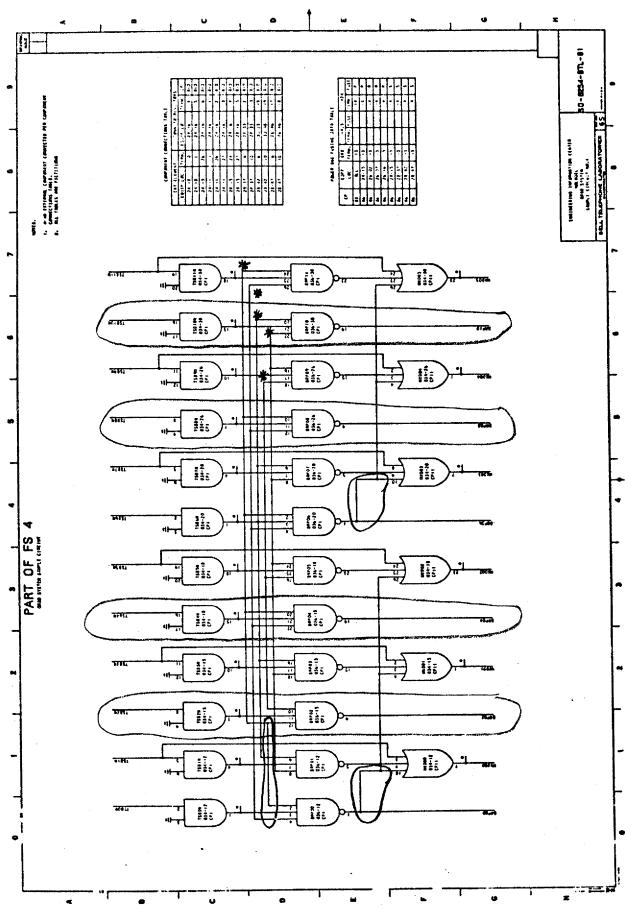

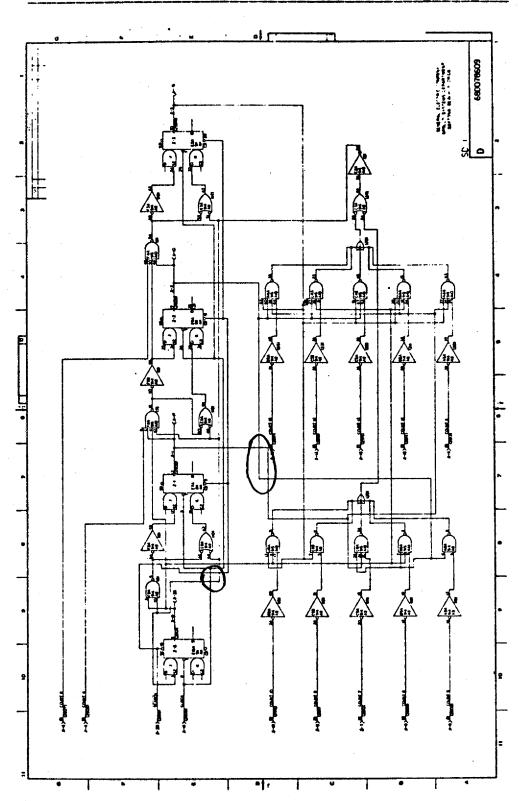

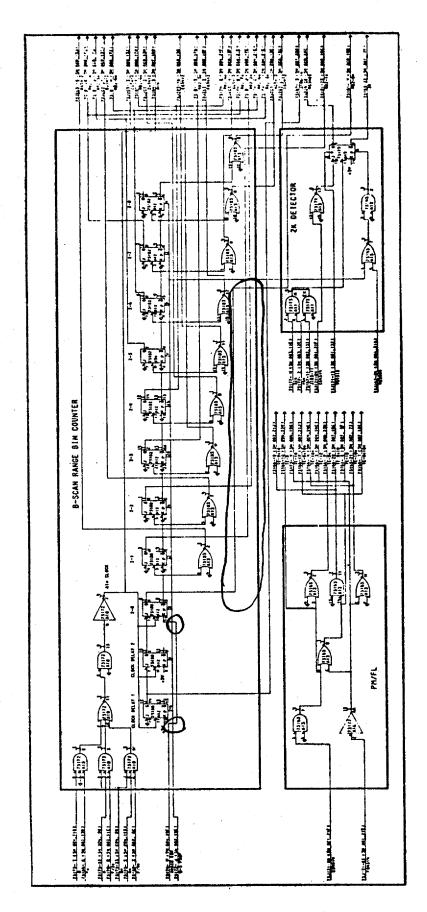

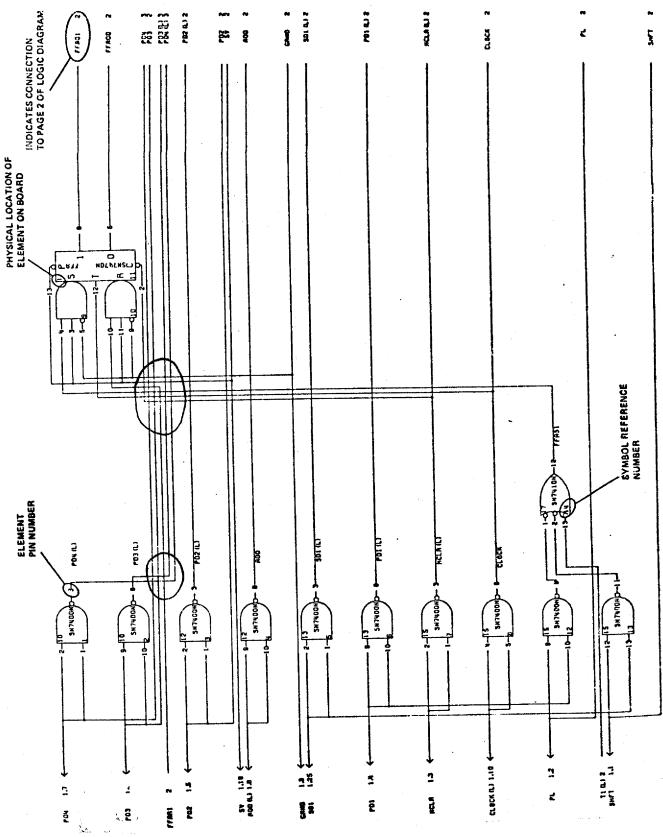

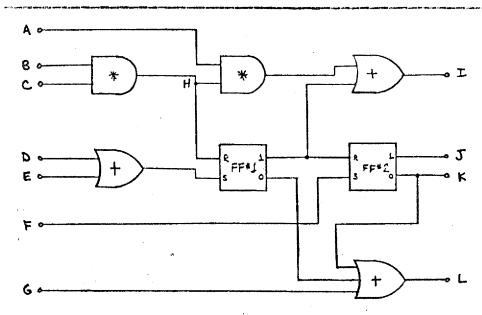

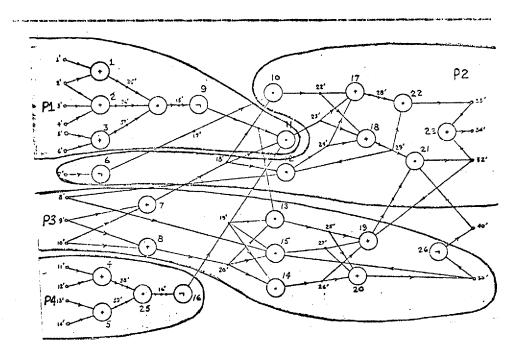

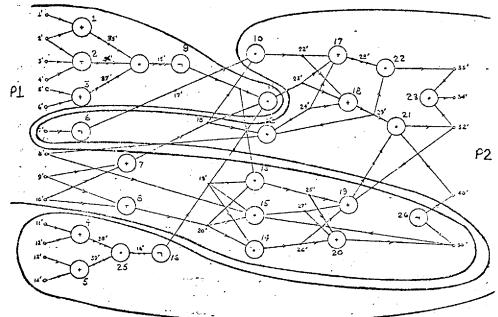

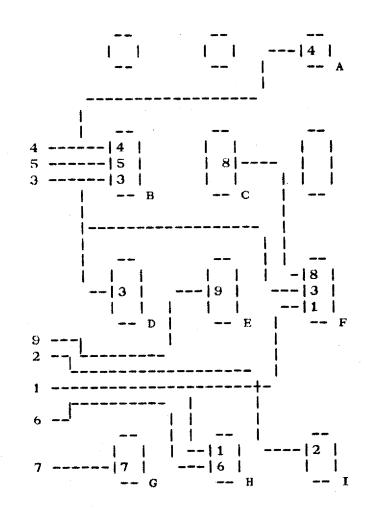

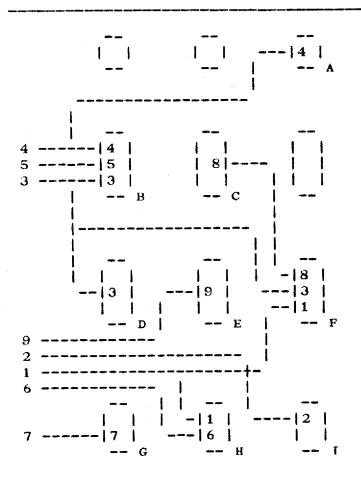

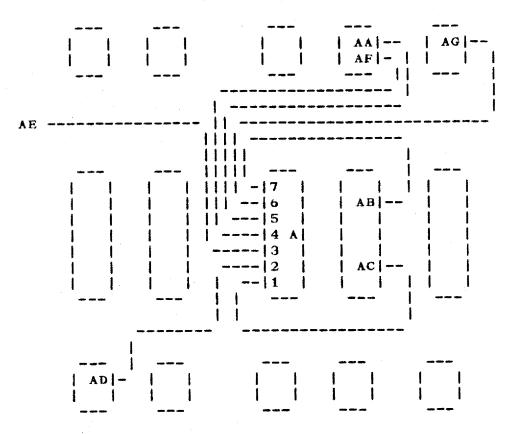

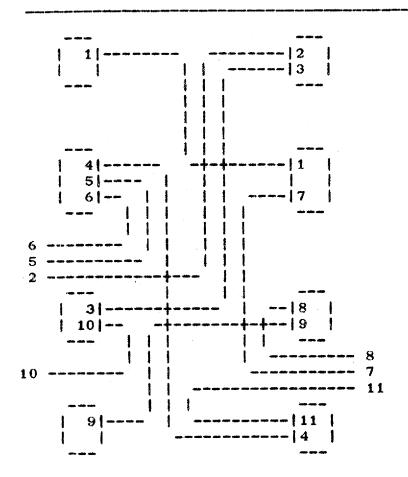

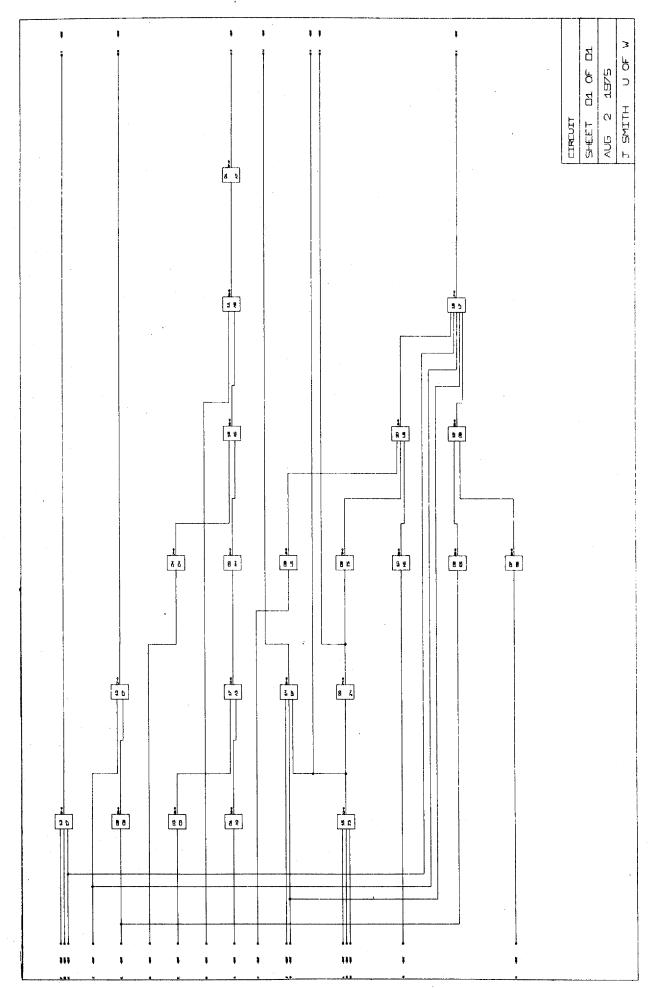

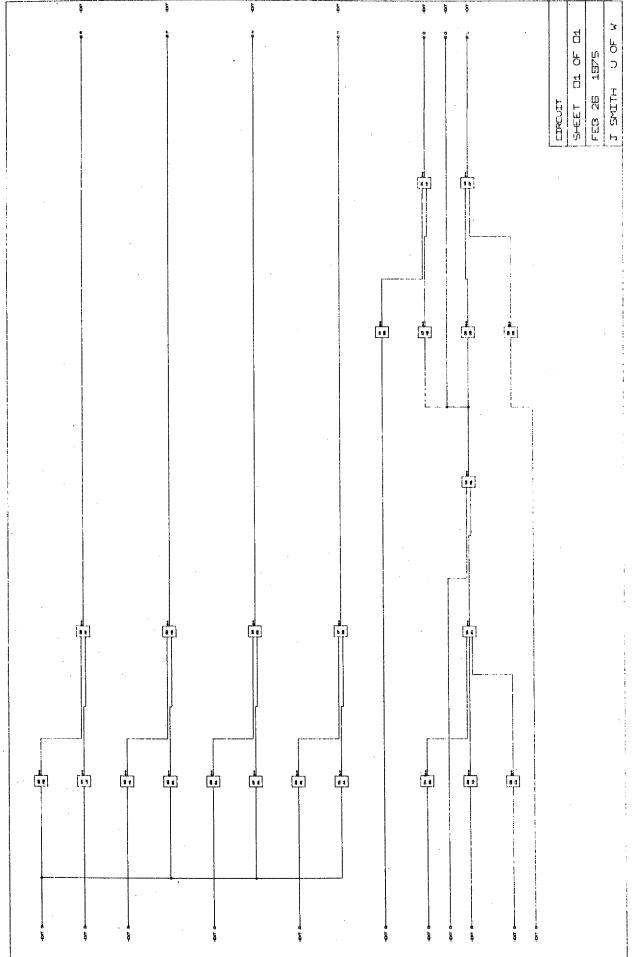

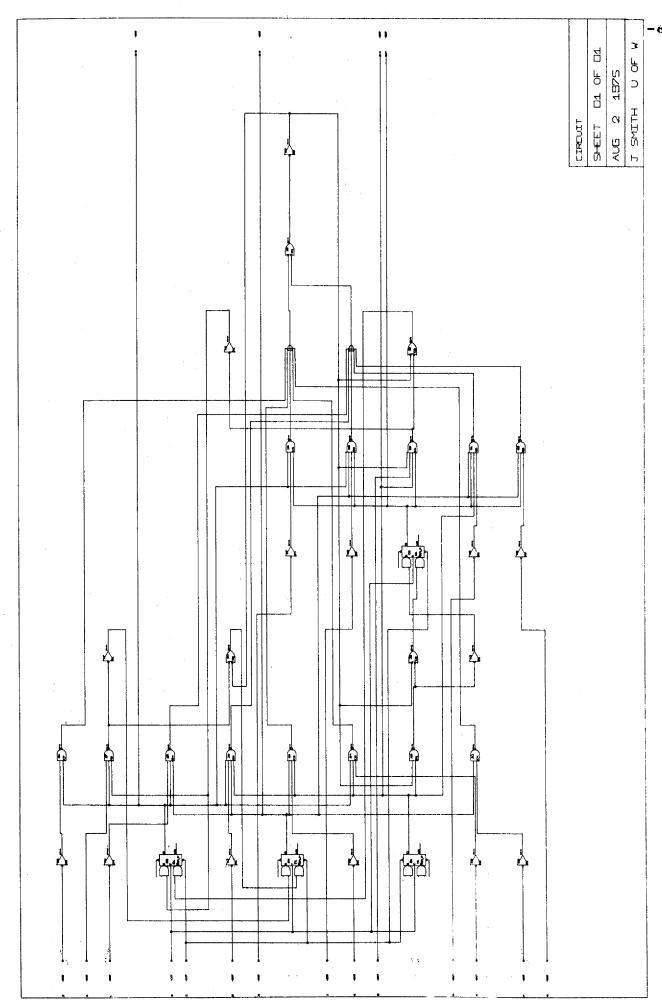

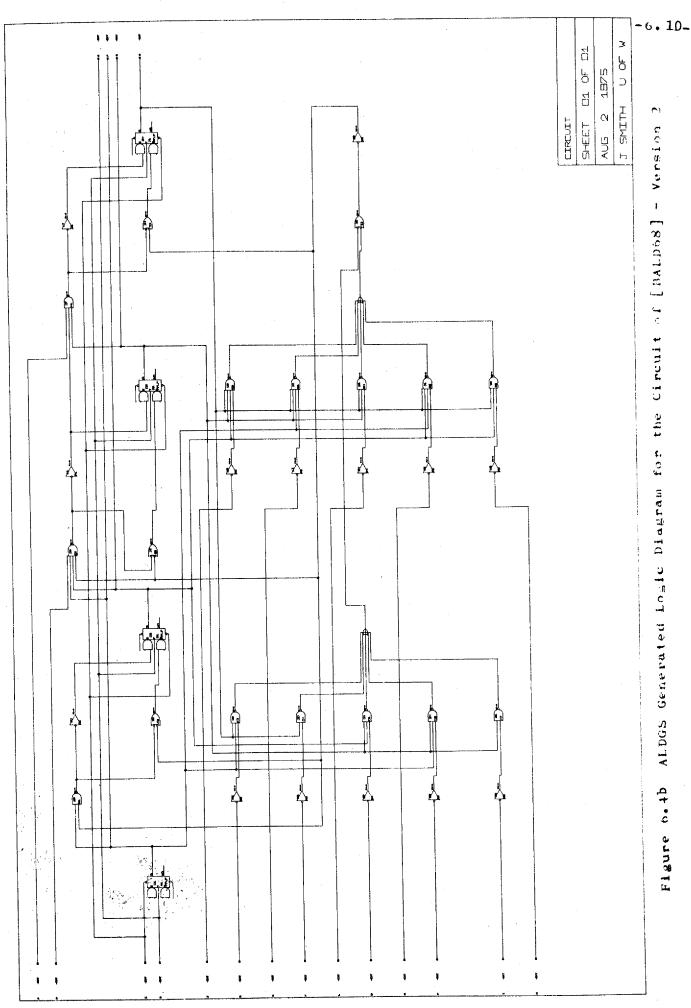

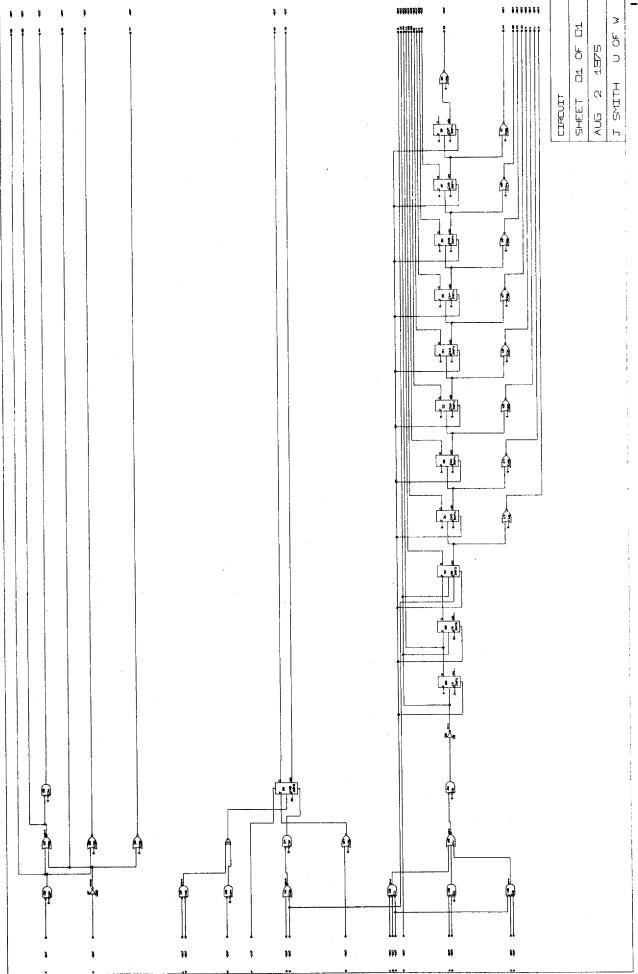

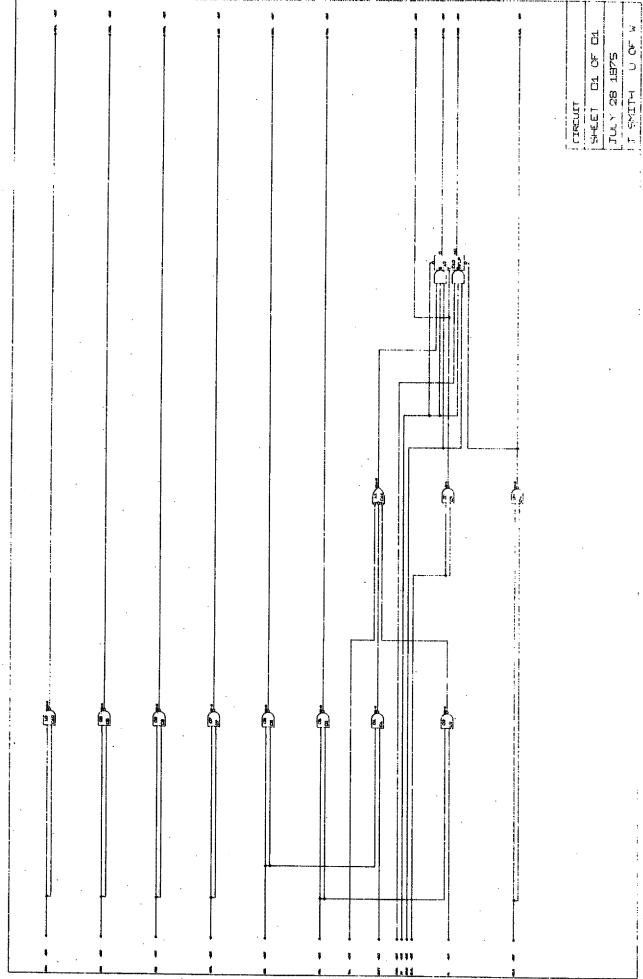

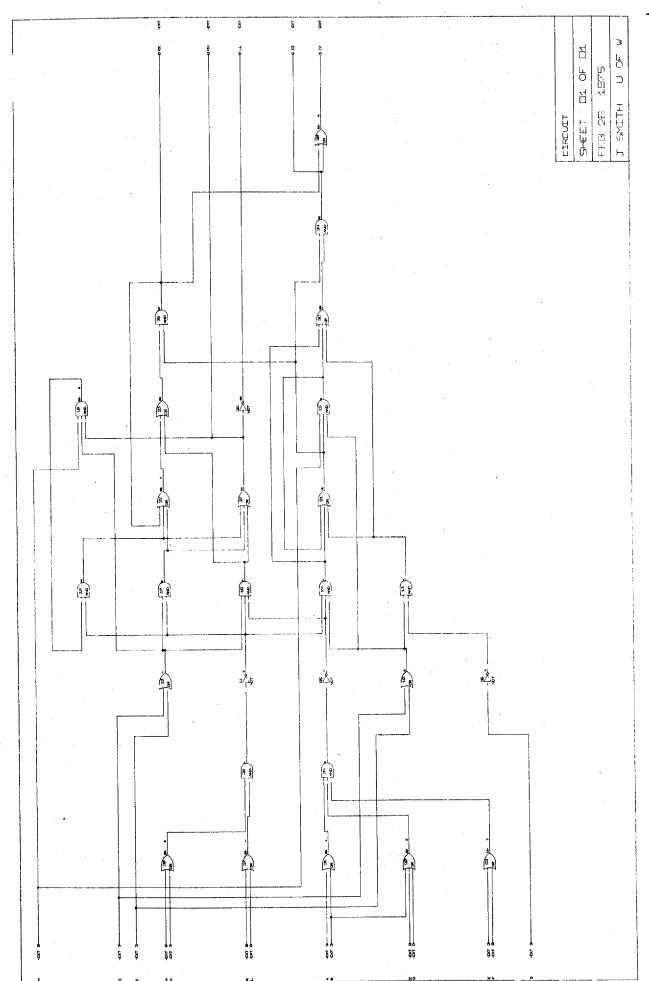

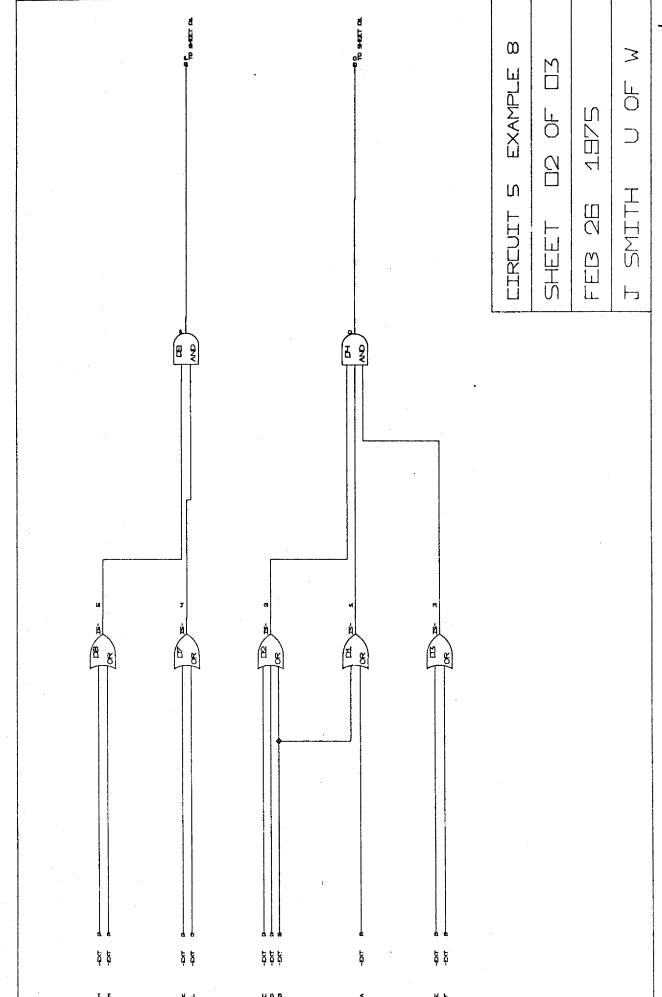

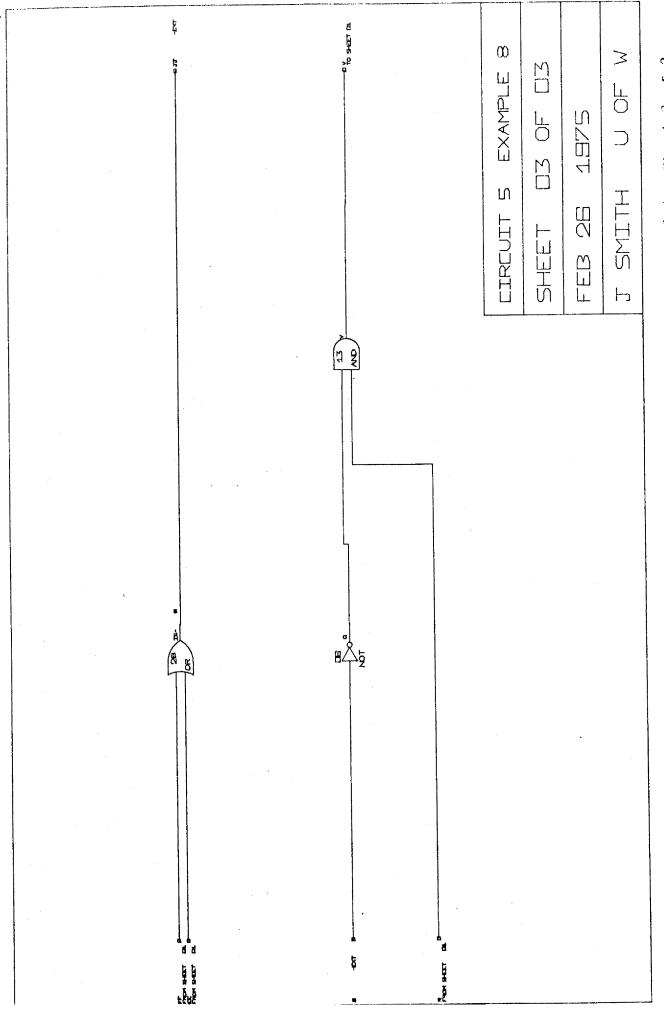

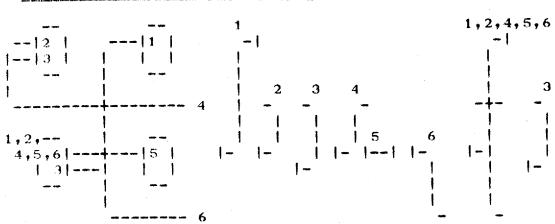

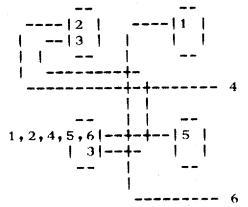

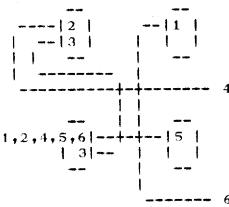

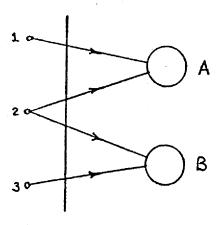

| 6.1 Samples of Automatically Produced Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6.1            |

| Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 001            |

| 6.2 Performance of ALDGS - Complexity of Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6.18           |

| 0.2 reriormance of Annon Comptexity of Augotivino                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>301</b>     |

| 6.3 Conculsions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.26           |

| O TO COMPOSE ON COMPOSE OF COMPOS |                |

| 6.4 Recommendations for Future Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.27           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| 6.5 Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| 6.5.1 Partitioning, Placement and Refinement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.28           |

| 6.5.2 Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6.29           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Appendix A. Classification of Signal Nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| A.1 Classification of the Signal Nodes of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Representative Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A • 1          |

| A.2 Classification of the Signal Nodes of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

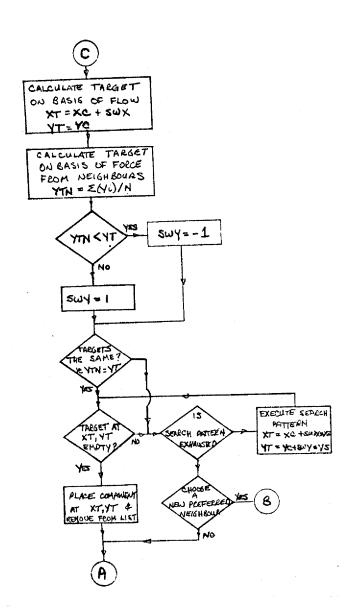

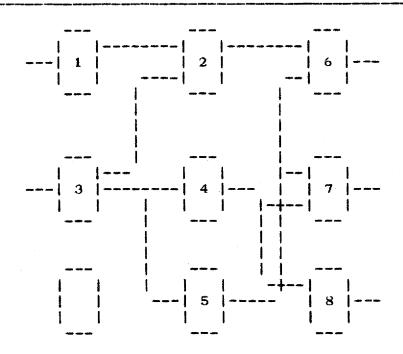

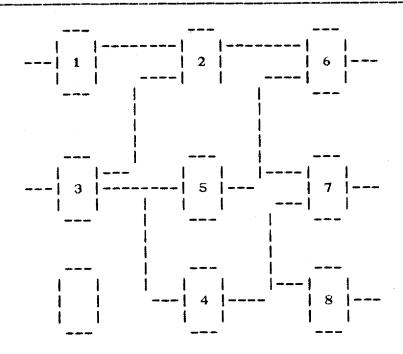

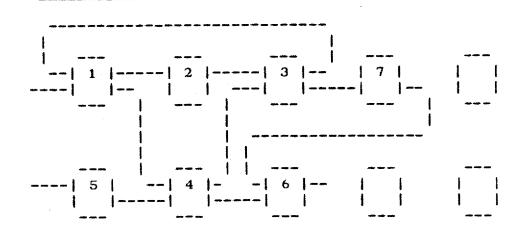

| of the Reduced Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A • 1          |